# IA-32 インテル® アーキテクチャソフトウェア・デベロッパーズ・マニュアル

#### 下巻:

システム・プログラミング・ガイド

#### 注記:

『IA-32 インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル』は、次の4巻から構成されています。

上巻:基本アーキテクチャ (資料番号 253665-013J) 中巻 A:命令セット・リファレンス A-M (資料番号 253666-013J) 中巻 B:命令セット・リファレンス N-Z (資料番号 253667-013J) 下巻:システム・プログラミング・ガイド (資料番号 253668-013J)

設計する際は、これら4巻すべてを参照してください。

2004年

#### 【輸出規制に関する告知と注意事項】

本資料に掲載されている製品のうち、外国為替および外国為替管理法に定める戦略物資等または役務に該当するものについては、輸出または再輸出する場合、同法に基づく日本政府の輸出許可が必要です。また、米国産品である当社製品は日本からの輸出または再輸出に際し、原則として米国政府の事前許可が必要です。

#### 【資料内容に関する注意事項】

- ・本ドキュメントの内容を予告なしに変更することがあります。

- ・ インテルでは、この資料に掲載された内容について、市販製品に使用した場合の保証あるいは特別な目的に合うことの保証等は、いかなる場合についてもいたしかねます。また、このドキュメント内の誤りについても責任を負いかねる場合があります。

- インテルでは、インテル製品の内部回路以外の使用にて責任を負いません。また、外部回路の特許についても関知いたしません。

- ・本書の情報はインテル製品を使用できるようにする目的でのみ記載されています。 インテルは、製品について「取引条件」で提示されている場合を除き、インテル製品の販売や使用に関して、いかなる特許または著作権の侵害をも含み、あらゆる責任を負わないものとします。

- ・ いかなる形および方法によっても、インテルの文書による許可なく、この資料の一部またはすべてを複写することは禁じられています。

IA-32 アーキテクチャ・プロセッサ (インテル® Pentium® 4 プロセッサ、インテル® Pentium® III プロセッサなど)、エラッタと呼ばれる設計上の不具合が含まれている可能性があり、公表されている仕様とは異なる動作をする場合があります。現在確認済みのエラッタについては、インテルまでお問い合わせください。

ハイパー・スレッディング・テクノロジを利用するには、ハイパー・スレッディング・テクノロジに対応したインテル Pentium 4 プロセッサを搭載したコンピュータ・システム、および同技術に対応したチップセットと BIOS、OS が必要です。性能は、使用するハードウェアやソフトウェアによって異なります。HT テクノロジに対応したプロセッサの情報等、詳細についてはhttp://www.intel.co.jp/jp/info/hyperthreading/を参照してください。

インテル、Intel ロゴ、Intel386、Intel486、Intel NetBurst、Celeron、MMX、Pentium、Intel SpeedStep、VTune、Xeon は、アメリカ合衆国およびその他の国における Intel Corporation またはその子会社の商標、登録商標です。

- \* その他の社名、製品名などは、一般に各社の商標または登録商標です。

- © 1997-2004, Intel Corporation.

# 目次

| 第 1 章 | 本書について                                                                               | 1-1          |

|-------|--------------------------------------------------------------------------------------|--------------|

|       | 1.1. 本書の対象となる IA-32 プロセッサ                                                            |              |

|       | 1.2. 『IA-32 インテル <sup>®</sup> アーキテクチャ・ソフトウェア・デベロッパーズ・マニュア<br>下巻:システム・プログラミング・ガイド』の概要 | 1-2          |

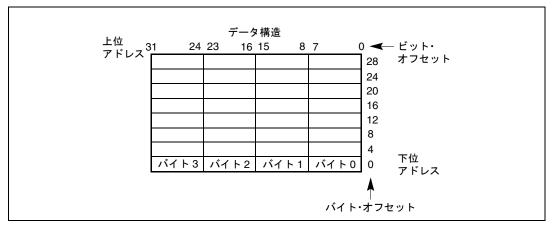

|       | 1.3. 表記法<br>1.3.1. ビット・オーダとバイト・オーダ                                                   | 1-4          |

|       | 1.3.1. ビット・オーダとパイト・オーダ                                                               | 1-5          |

|       | 1.3.2. 予約ビットとソフトリェアの互換性                                                              |              |

|       | 1.3.4. 16 進と 2 進数                                                                    |              |

|       | 1.3.5. セグメント化アドレス指定                                                                  |              |

|       | 1.3.6. 例外                                                                            |              |

|       | 1.4. 参考文献                                                                            | 1-8          |

|       | 1.5. 参考 URL                                                                          | 1-9          |

| 第2章   | システム・アーキテクチャの概要                                                                      | 2-1          |

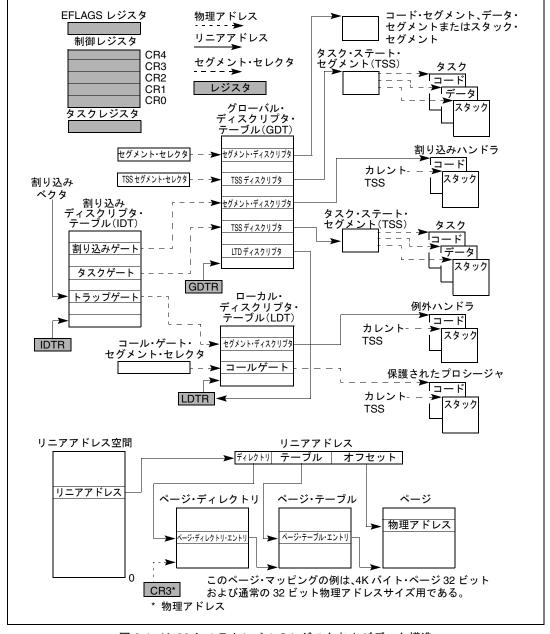

|       | 2.1. システム・レベル・アーキテクチャの概要                                                             |              |

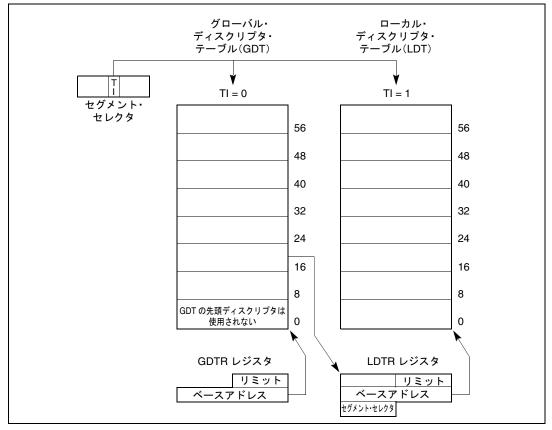

|       | 2.1.1. グローバル・ディスクリプタ・テーブルとローカル・ディスクリプタ・<br>テーブル                                      |              |

|       | 2.1.2. システム・セグメント、セグメント・ディスクリプタ、ゲート                                                  | 2-3<br>2-3   |

|       | 2.1.3. タスク・ステート・セグメントとタスクゲート                                                         | 2-4          |

|       | 2.1.4. 割り込み / 例外処理                                                                   | 2-5          |

|       | 2.1.5. メモリ管理                                                                         |              |

|       | 2.1.6. システムレジスタ                                                                      |              |

|       | 2.1.7. その他のシステムリソース                                                                  |              |

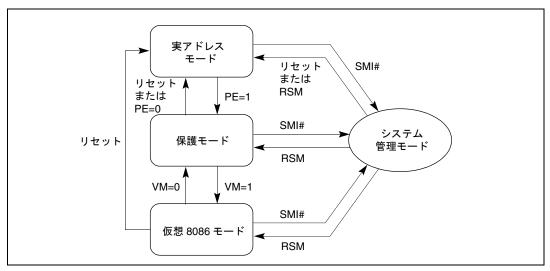

|       | 2.2. 動作モード                                                                           |              |

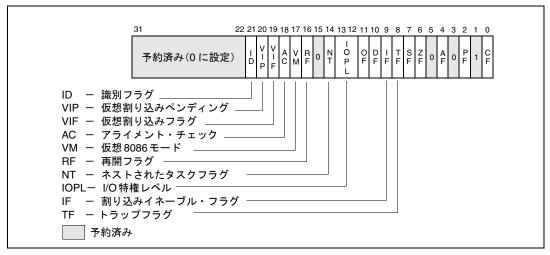

|       | 2.3. EFLAGS レジスタのシステムフラグとフィールド                                                       |              |

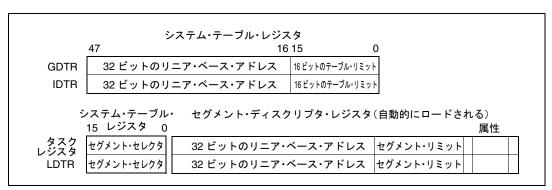

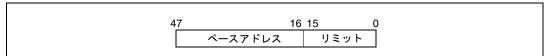

|       | 2.4. メモリ管理レジスタ<br>2.4.1. グローバル・ディスクリプタ・テーブル・レジスタ(GDTR)                               | 2-12         |

|       | 2.4.1. グローバル・ディスクリプタ・テーブル・レジスタ (GDTR)<br>2.4.2. ローカル・ディスクリプタ・テーブル・レジスタ (LDTR)        |              |

|       | 2.4.2. 目 カル・ティステリプタ・テーブル・レジスタ (IDTR)                                                 | 2-13<br>2-13 |

|       | 2.4.4. タスクレジスタ (TR)                                                                  | 2-13         |

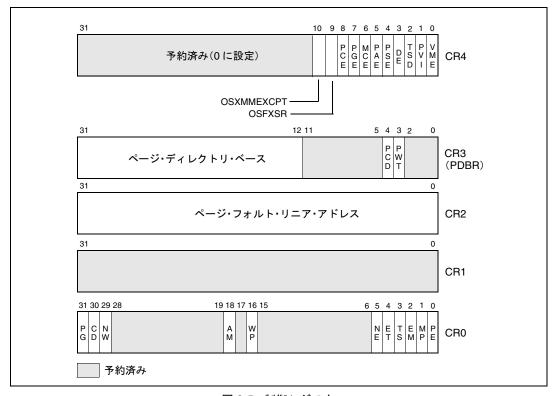

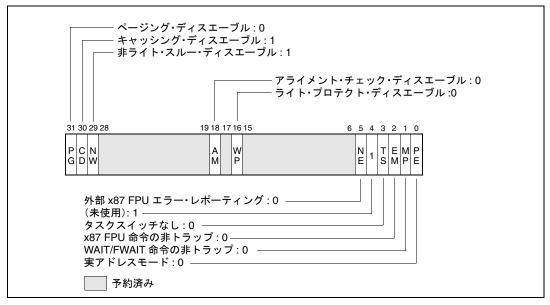

|       | 2.5. 制御レジスタ                                                                          | 2-14         |

|       | 2.5.1. 制御レジスタフラグの CPUID 確認                                                           | 2-22         |

|       | 2.6. システム命令のまとめ                                                                      | 2-22         |

|       | 2.6.1. システムレジスタのロードとストア                                                              |              |

|       | 2.6.2. アクセス特権の確認                                                                     | 2-25         |

|       | 2.6.3. デバッグレジスタのロードとストア                                                              | 2-26         |

|       | 2.6.4. キャッシュと TLB の無効化<br>2.6.5. プロセッサの制御                                            |              |

|       | 2.6.6. 性能モニタリング・カウンタとタイムスタンプ・カウンタの読み取り                                               | 2-20<br>2-27 |

|       | 2.6.7. モデル固有レジスタの読み取りと書き込み                                                           | 2-28         |

| 笠の辛   | <b>小菜エードルナスチェリ英</b> 亜                                                                | 0.1          |

| おう早   | 保護モードにおけるメモリ管理                                                                       |              |

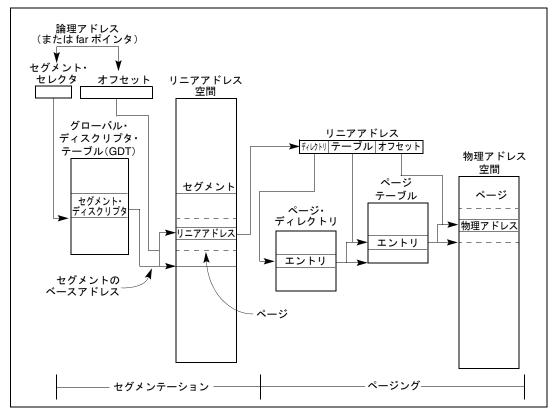

|       | 3.1. メモリ管理の概要                                                                        |              |

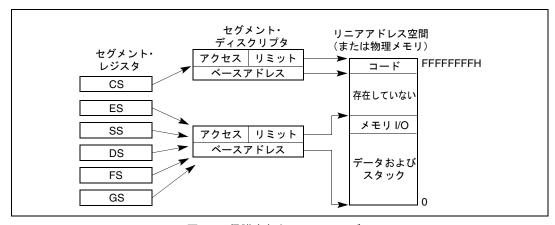

|       | 3.2. セクメントの使用法                                                                       |              |

|       | 3.2.2. 保護されたフラットモデル                                                                  | 3-4          |

|       | 3.2.3. マルチセグメント・モデル                                                                  | 3-6          |

|       | 3.2.4. ページングとセグメンテーション                                                               | 3-7          |

|       | 3.3. 物理アドレス空間                                                                        |              |

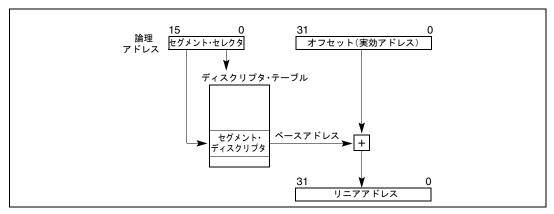

|       | 3.4. 論理アドレスとリニアアドレス                                                                  |              |

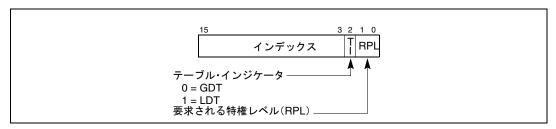

|       | 3.4.1. セグメント・セレクタ                                                                    | 3-9          |

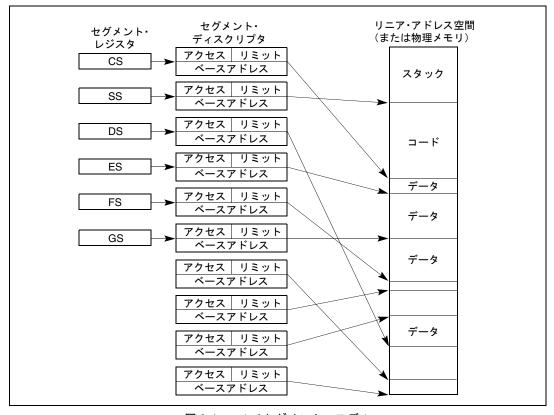

|     | 3.4.2. セグメント・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-10                                                               |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

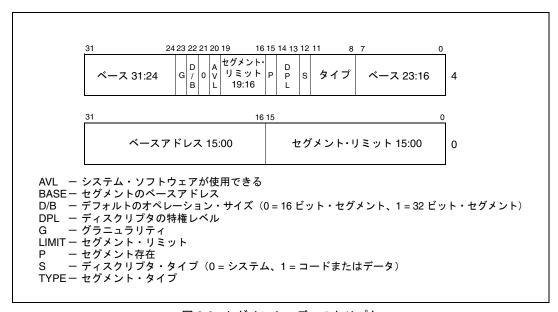

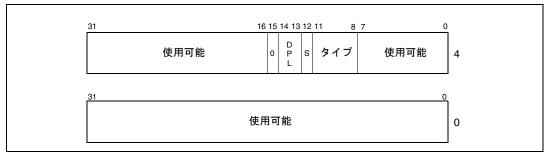

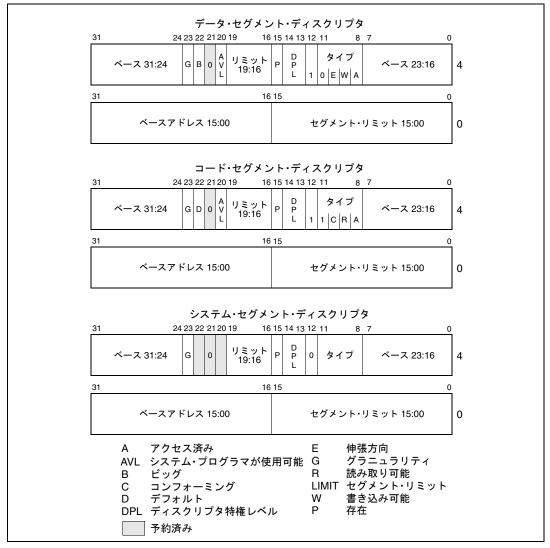

|     | 3.4.3. セグメント・ディスクリプタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-12                                                               |

|     | 3.4.3.1. セグメント・ディスクリプタのタイプ - コードとデータ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

|     | 3.5. システム・ディスクリプタ・タイプ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-18                                                               |

|     | 3.5.1. セグメント・ディスクリプタ・テーブル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-19                                                               |

|     | 3.6. ページング(仮想メモリ)の概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-22                                                               |

|     | 3.6.1. ページングのオプション                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-23                                                               |

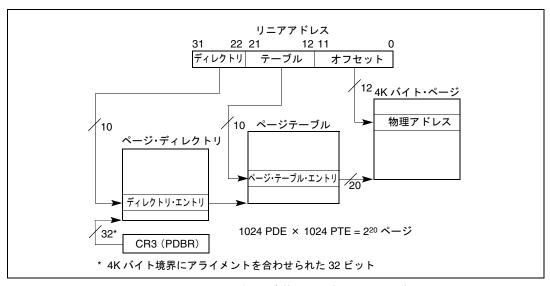

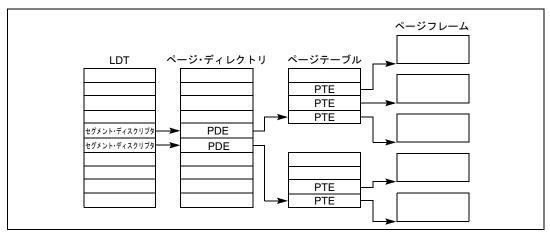

|     | 3.6.2. ページテーブルとページ・ディレクトリ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-24                                                               |

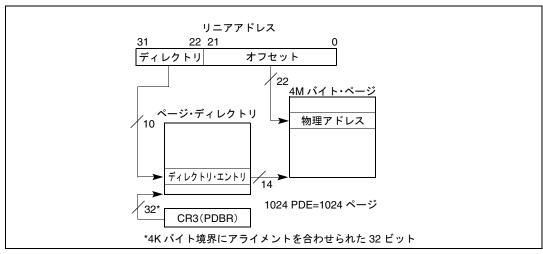

|     | 3.7. 32 ビット物理アドレス指定を使用したページ変換                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-24                                                               |

|     | 3.7.1. リニアアドレス変換 (4K バイト・ページ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-25                                                               |

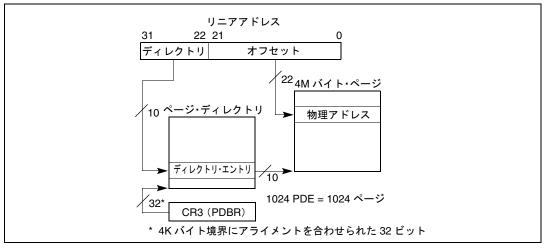

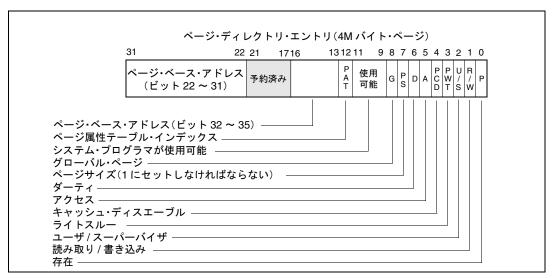

|     | 3.7.2. リニアアドレス変換(4M バイト・ページ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-26                                                               |

|     | 3.7.3. 4K バイト・ページと 4M バイト・ページの混在                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

|     | 3.7.4. メモリ別名定義                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-28                                                               |

|     | 3.7.5. ページ・ディレクトリのベースアドレス                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-28                                                               |

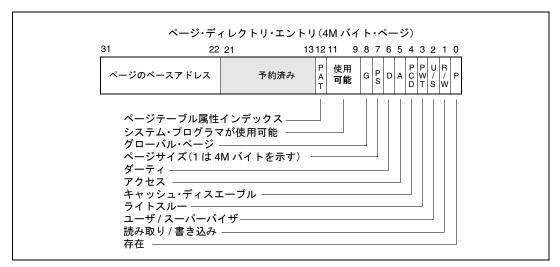

|     | 3.7.6. ページ・ディレクトリ・エントリとページ・テーブル・エントリ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-28                                                               |

|     | 3.7.7. 存在していないページ・ディレクトリ・エントリと<br>ページ・テーブル・エントリ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.04                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-34                                                               |

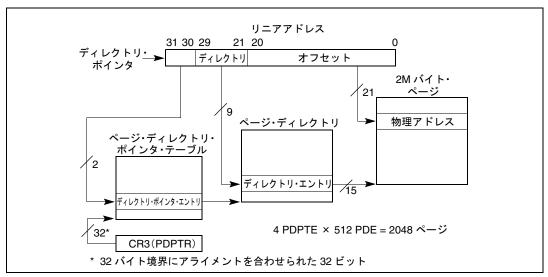

|     | 3.8. PAE ページング・メカニズムを使用した 36 ビット物理アドレス指定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-35                                                               |

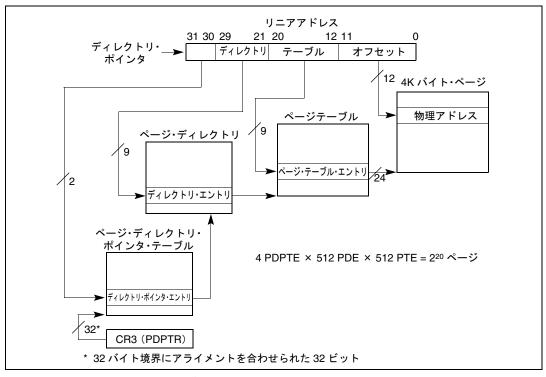

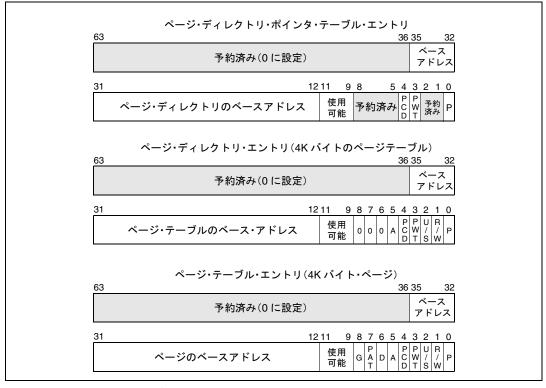

|     | 3.8.1. PAE がイネーブルの場合のリニアアドレス変換(4K バイト・ページ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |

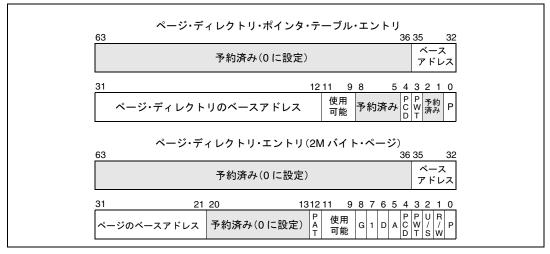

|     | 3.8.2. PAE がイネーブルの場合のリニアアドレス変換(2M バイト・ページ)<br>3.8.3. 拡張ページテーブル構造を使用した拡張物理アドレス空間全体への                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-37                                                               |

|     | 3.6.3. 協張ページナーブル構造を使用した拡張物理プトレス空间主体への<br>アクセス                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-30                                                               |

|     | 3.8.4. 拡張アドレス指定がイネーブルの場合のページ・ディレクトリ・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-50                                                               |

|     | エントリとページ・テーブル・エントリ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-39                                                               |

|     | 3.9. PSE-36 ページング・メカニズムを使用した 36 ビット物理アドレス指定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

|     | 3.10. ページへのセグメントのマッピング                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|     | 3.11. トランスレーション・ルックアサイド・バッファ(TLB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-45                                                               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

| 第4章 | 保護                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1                                                                |

|     | 4.1. セグメントとページの保護の有効化 / 無効化                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-2                                                                |

|     | 4.2. セグメント・レベルとページレベルの保護に使用されるフィールドとフラグ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-2                                                                |

|     | 4.3. リミットチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-5                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|     | 4.4. タイプチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-6                                                                |

|     | 4.4. タイプチェック<br>4.4.1. ヌル・セグメント・セレクタ・チェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-6<br>4-8                                                         |

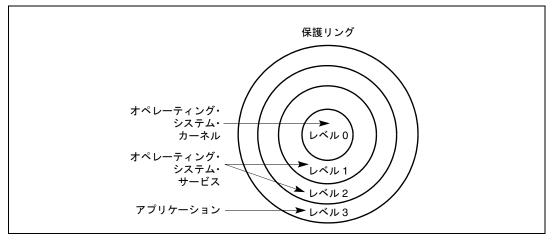

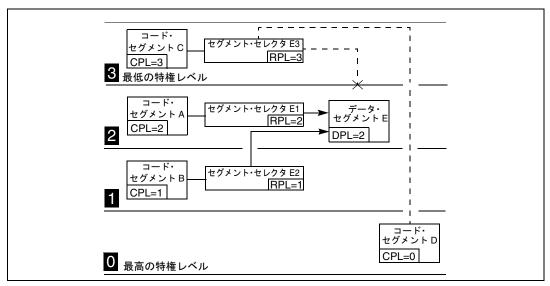

|     | 4.4. タイプチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-6<br>4-8<br>4-9                                                  |

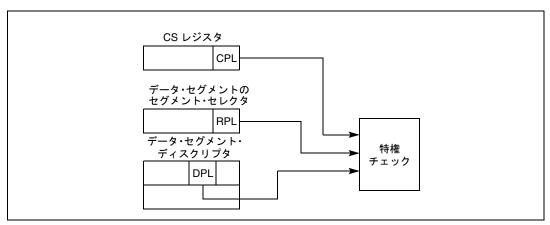

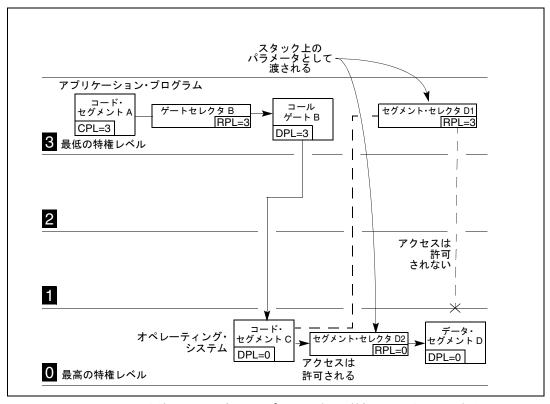

|     | 4.4. タイプチェック         4.4.1. ヌル・セグメント・セレクタ・チェック         4.5. 特権レベル         4.6. データ・セグメントにアクセスする際の特権レベルチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-6<br>4-8<br>4-9<br>4-11                                          |

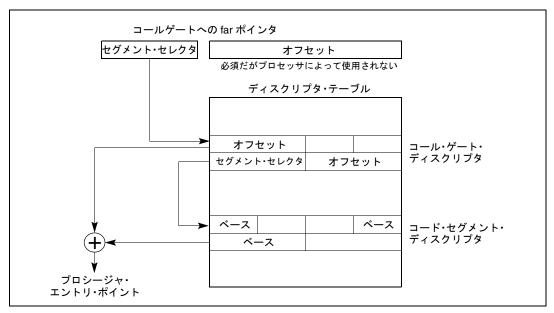

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-9<br>4-11<br>4-14                                  |

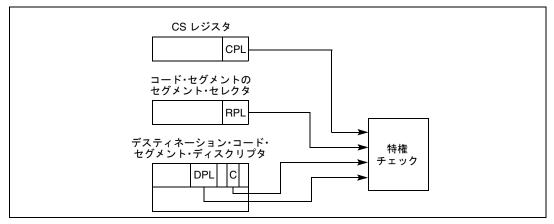

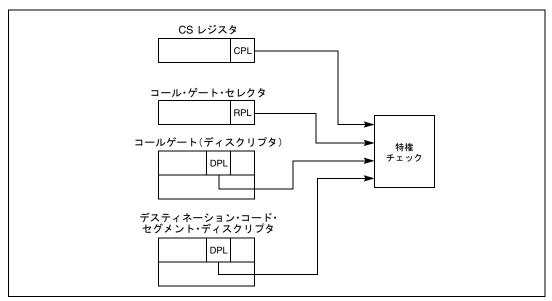

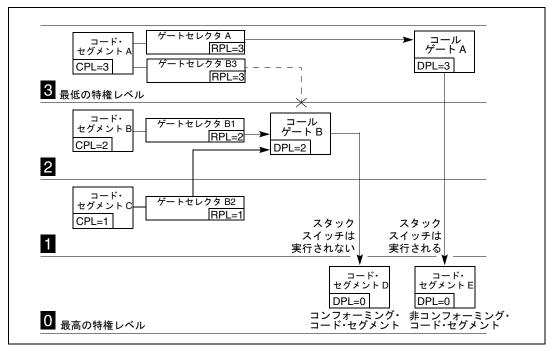

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-9<br>4-11<br>4-14                                  |

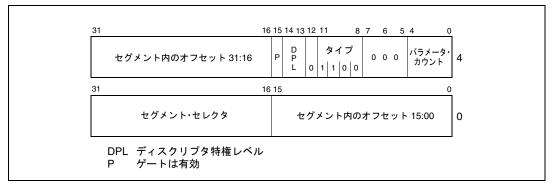

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-9<br>4-14<br>4-14                                  |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-11<br>4-14<br>4-14<br>4-15                         |

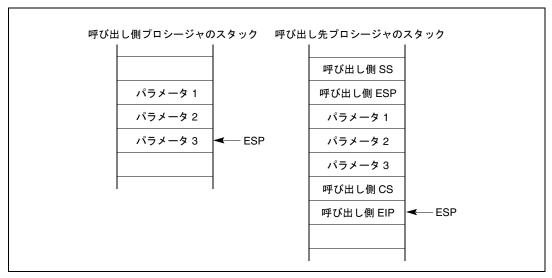

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-11<br>4-14<br>4-14<br>4-15                         |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-9<br>4-14<br>4-14<br>4-15<br>4-16                  |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-11<br>4-14<br>4-14<br>4-15<br>4-16<br>4-18         |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-11<br>4-14<br>4-14<br>4-15<br>4-16<br>4-18<br>4-19 |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6<br>4-8<br>4-11<br>4-14<br>4-15<br>4-16<br>4-18<br>4-19         |

|     | 4.4. タイプチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-64-94-114-144-144-164-194-194-21                                 |

|     | 4.4. タイプチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-64-94-114-144-144-164-194-194-21                                 |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-64-94-114-144-144-164-194-214-28                                 |

|     | 4.4. タイプチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-64-94-114-144-144-154-194-194-21                                 |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-64-94-114-144-154-164-194-214-284-29                             |

|     | 4.4. タイプチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-64-114-144-144-164-194-214-284-28                                |

|     | <ul> <li>4.4. タイプチェック</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-64-114-144-144-164-194-214-284-284-32                            |

|     | 4.4. タイプチェック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-64-114-144-154-164-184-194-284-314-324-324-334-324-33            |

|     | 4.4. タイプチェック         4.4.1. ヌル・セグメント・セレクタ・チェック         4.5. 特権レベル         4.6. データ・セグメントにアクセスする際の特権レベルチェック         4.6.1. コード・セグメント内のデータへのアクセス         4.7. SS レジスタにロードする際の特権レベルチェック         4.8. コード・セグメント間でプログラム制御を移行する際の特権レベルチェック         4.8.1. コード・セグメントへの直接呼び出しまたはジャンプ         4.8.1.1. 非コンフォーミング・コード・セグメントへのアクセス         4.8.2. ゲート・ディスクリプタ         4.8.3. コールゲート         4.8.4. コールゲートを通じたコード・セグメントへのアクセス         4.8.5. スタック・スイッチング         4.8.6. 呼び出し先プロシージャからの戻り         4.8.7. SYSENTER 命令と SYSEXIT 命令によるシステム・プロシージャへの高速呼び出しの実行         4.9. 特権命令         4.10.ポインタの妥当性チェック         4.10.1. アクセス権のチェック (LAR 命令)         4.10.2. 読み取り/書き込み権のチェック (VERR 命令と VERW 命令)         4.10.3. ポインタ・オフセットがリミット内にあるかどうかのチェック (LSL 命令)         4.10.4. 呼び出し側のアクセス特権のチェック (ARPL 命令) | 4-64-114-144-154-184-194-214-284-314-32                            |

|     | 4.11. ページレベルの保護                                        | 4-37         |

|-----|--------------------------------------------------------|--------------|

|     | 4.11.1. ページ保護フラグ                                       | 4-38         |

|     | 4.11.2. アドレス指定可能ドメインの制限                                |              |

|     | 4.11.3. ページタイプ                                         | 4-39         |

|     | 4.11.4. ページテーブルの 2 つのレベルの保護の組み合わせ                      | 4-40         |

|     | 4.11.5. ページ保護のオーバーライド                                  |              |

|     | 4.12.ページ保護とセグメント保護の組み合わせ                               | 4-40         |

| 第5章 | 割り込みと例外の処理                                             | 5-1          |

|     | 5.1. 割り込みと例外の概要                                        | 5-1          |

|     | 5.2. 例外ベクタと割り込みベクタ                                     |              |

|     | 5.3. 割り込みのソース                                          | 5-2          |

|     | 5.3.1. 外部割り込み                                          | 5-3          |

|     | 5.3.2. マスク可能ハードウェア割り込み                                 | 5-5          |

|     | 5.3.3. ソフトウェア生成割り込み                                    |              |

|     | 5.4. 例外のソース                                            |              |

|     | 5.4.1. プログラム・エラー例外                                     |              |

|     | 5.4.2. ソフトウェア生成例外                                      |              |

|     |                                                        |              |

|     | 5.5. 例外の分類                                             |              |

|     | 5.6. プログラムまたはタスクの再スタート                                 |              |

|     | 5.7. マスク不可能割り込み(NMI: Nonmaskable Interrupt)            |              |

|     | 5.7.1. 複数の NMI の処理                                     |              |

|     | 5.8. 割り込みのイネーブル / ディスエーブル                              | 5-10         |

|     | 5.8.2. 命令ブレークポイントのマスキング                                | 5-10<br>5-11 |

|     | 5.8.3. スタック切り替え時に行われる例外と割り込みのマスキング                     | 5-12         |

|     | 5.9. 同時に発生した例外や割り込みの間の優先順位                             |              |

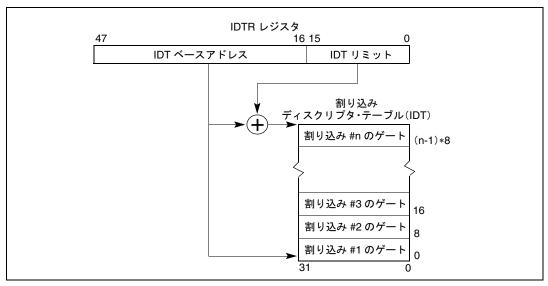

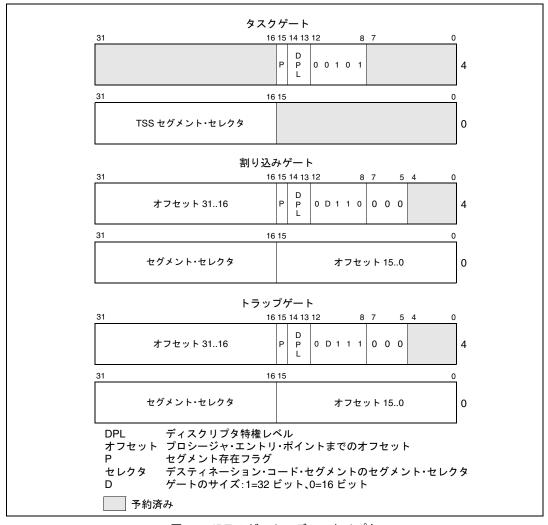

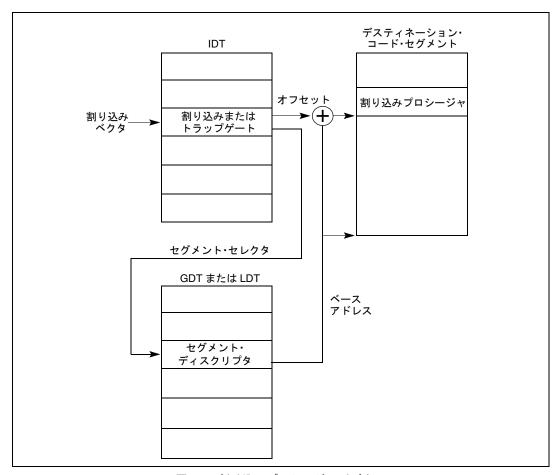

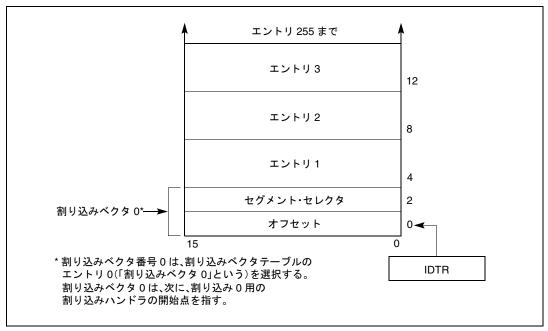

|     | 5.10.割り込みディスクリプタ・テーブル(IDT: Interrupt Descriptor Table) |              |

|     | 5.11.IDT ディスクリプタ                                       |              |

|     | 5.11.101 / イスノリング                                      |              |

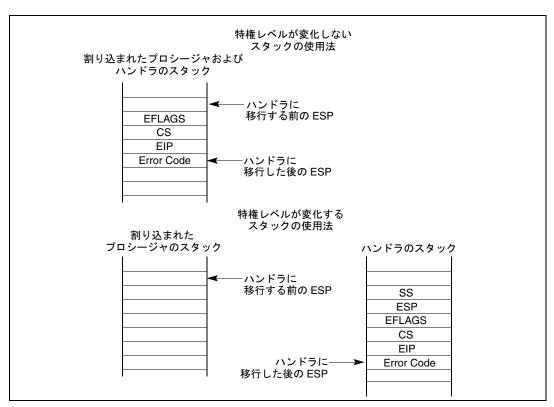

|     | 5.12.1. 例外 / 割り込みハンドラ・プロシージャ                           | 5-17         |

|     | 5.12.1.1. 例外 / 割り込みハンドラ・プロシージャの保護                      | 5-19         |

|     | 5.12.1.2. 例外/割り込みハンドラ・プロシージャによるフラグの使用法                 | 5-20         |

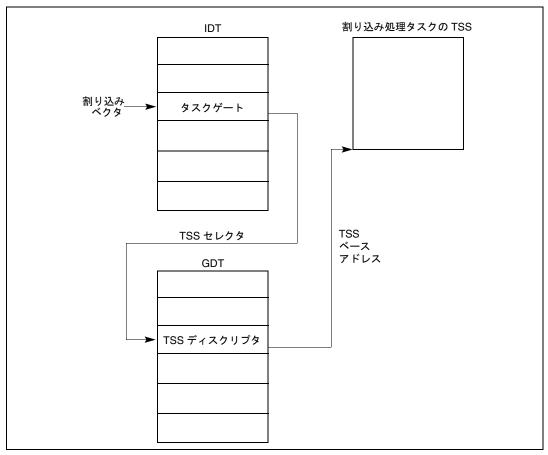

|     | 5.12.2. 割り込みタスク                                        | 5-20         |

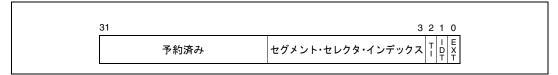

|     | 5.13.エラーコード                                            | 5-23         |

|     | 5.14. 例外と割り込みのリファレンス                                   | 5-24         |

|     | 割り込み 0 - 除算エラー例外(#DE)                                  | 5-25         |

|     | 割り込み 1 ーデバッグ例外(#DB)                                    | 5-26         |

|     | 割り込み 2 ー NMI 割り込み割り込み 3 ーブレークポイント例外(#BP)               | 5-27         |

|     | 割り込み 4 ーオーバーフロー例外(#OF)<br>割り込み 4 ーオーバーフロー例外(#OF)       |              |

|     | 割り込み 5 — BOUND 範囲超過例外(#BR)                             | 5-30         |

|     | 割り込み 6 一無効オペコード例外 (#UD)                                | 5-31         |

|     | 割り込み7-デバイス使用不可例外(#NM)                                  | 5-33         |

|     | 割り込み 8 -ダブルフォルト例外(#DF)                                 | 5-35         |

|     | 割り込み9ーコプロセッサ・セグメント・オーバーラン                              |              |

|     | 割り込み 10 一無効 TSS 例外(#TS)<br>割り込み 11 ーセグメント不在例外(#NP)     |              |

|     | 割り込み 11 ーセクメント个任例外(#NP)<br>割り込み 12 ースタックフォルト例外(#SS)    |              |

|     | 割り込み 13 — 一般保護例外 (#GP)                                 |              |

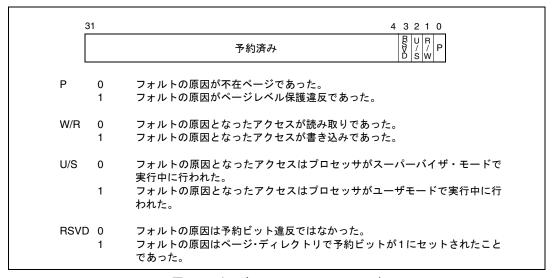

|     | 割り込み 14 -ページフォルト例外(#PF)                                |              |

|     | 割り込み 16 - x87 FPU 浮動小数点エラー (#MF)                       | 5-53         |

|     | 割り込み 17 - アライメント・チェック例外(#AC)                           |              |

|     | 割り込み 18 ーマシンチェック例外(#MC)<br>割り込み 19 ー SIMD 浮動小数占例外(#XF) | 5-59<br>5-61 |

|     | =11.0.1へか、19 − 51MD (Z.WI/N.W) 中10H/VN(#X上)            | n-h1         |

|     | 割り込み 32 ~ 255 -ユーザ定義の割り込み                                         | 5-64 |

|-----|-------------------------------------------------------------------|------|

| 第6章 | タスク管理                                                             | 6-1  |

|     | 6.1. タスク管理の概要                                                     | 6-1  |

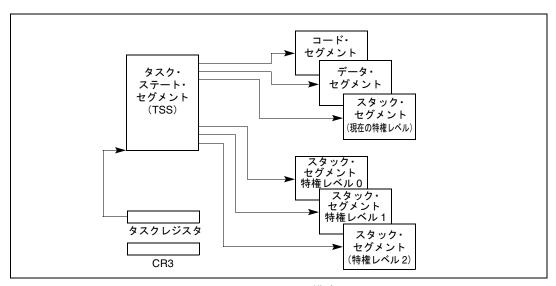

|     | 6.1.1. タスクの構造                                                     |      |

|     | 6.1.2. タスクのステート                                                   | 6-2  |

|     | 6.1.3. タスクの実行                                                     | 6-3  |

|     | 6.2. タスク管理用データ構造                                                  | 6-5  |

|     | 6.2.1. タスク・ステート・セグメント (TSS)                                       | 6-5  |

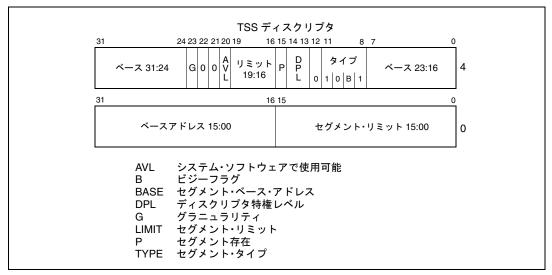

|     | 6.2.2. TSS ディスクリプタ                                                |      |

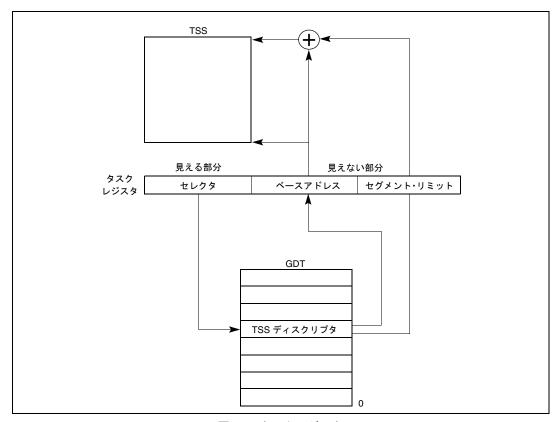

|     | 6.2.3. タスクレジスタ                                                    | 6-10 |

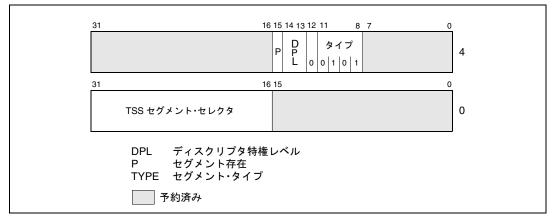

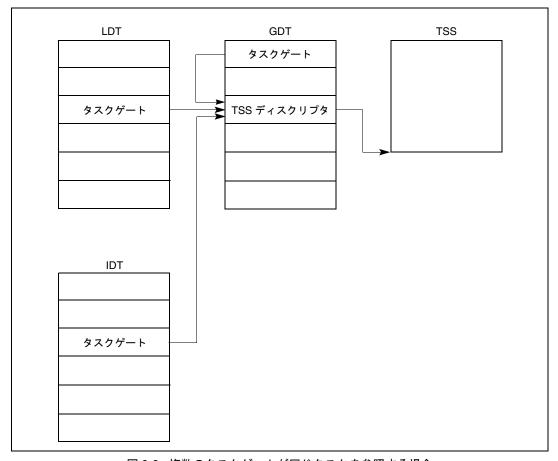

|     | 6.2.4. タスク・ゲート・ディスクリプタ                                            | 6-10 |

|     | 6.3. タスク・スイッチング                                                   | 6-13 |

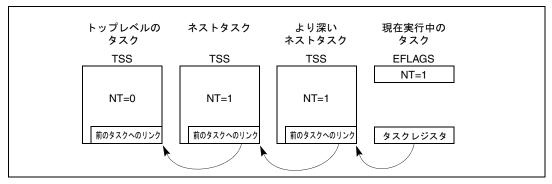

|     | 6.4. タスクのリンク                                                      | 6-17 |

|     | 6.4.1. ビジーフラグを使用したリカーシブ・タスク・スイッチの防止                               | 6-19 |

|     | 6.4.2. タスク・リンケージの変更                                               |      |

|     | 6.5. タスクアドレス空間                                                    |      |

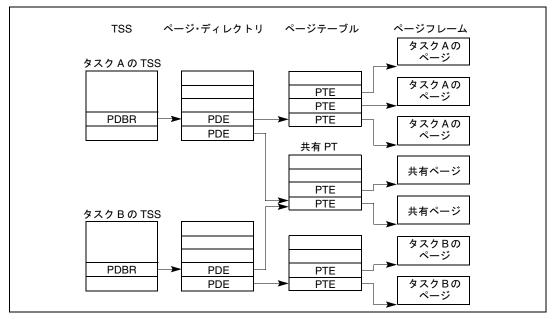

|     | 6.5.1. タスクのリニアー物理アドレス空間へのマッピング                                    | 6-21 |

|     | 6.5.2. タスクの論理アドレス空間                                               |      |

|     | 6.6. 16 ビットのタスク・ステート・セグメント (TSS)                                  | 6-23 |

|     | 0.0. 10 2 7 1 0 7 7 7 1 2 7 7 7 1 100/                            | 0 20 |

| 第7章 | マルチプロセッサ管理                                                        | 7-1  |

|     | 7.1. ロックされたアトミック操作                                                | 7-2  |

|     | 7.1.1. 保証付きアトミック操作                                                | 7-3  |

|     | 7.1.2. バスのロック                                                     |      |

|     | 7.1.2.1. 自動バスロック                                                  | 7-4  |

|     | 7.1.2.2. ソフトウェア制御されたバスロック                                         | 7-5  |

|     | 7.1.3. 自己修正コードおよびクロス修正コードの処理                                      | 7-7  |

|     | 7.1.4. プロセッサ内部キャッシュ上のロック操作                                        | 7-8  |

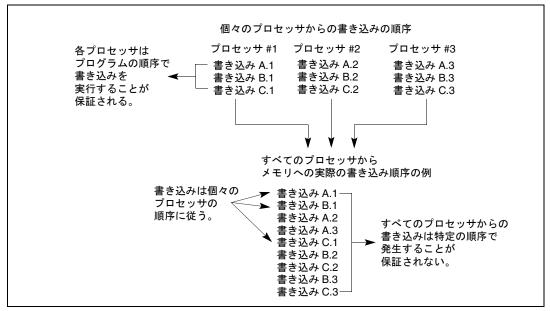

|     | 7.2. メモリ・オーダリング                                                   | 7-9  |

|     | 7.2.1. インテル® Pentium® プロセッサおよび Intel486™ プロセッサでの<br>メモリ・オーダリング    | 7.0  |

|     | 7.2.2. インテル® Pentium® 4 プロセッサ、インテル® Xeon™ プロセッサ、                  | /-8  |

|     | 7.2.2. インナル® Penilum® 4 ノロセッサ、インナル® Xeon'™ ノロセッサ、                 | 7 10 |

|     | P6 ファミリ・プロセッサでのメモリ・オーダリング                                         | 7-10 |

|     | P6 ファミリ・プロセッサでのストリングからの                                           |      |

|     | P6 ファミリ・プロセッサでのストリングからの<br>アウト・オブ・オーダー・ストア操作                      | 7-12 |

|     | 7.2.4. メモリ・オーダリング・モデルのストロング・オーダリング/                               | 7-12 |

|     | ウィーク・オーダリング                                                       | 7-13 |

|     | 7.3. 複数のプロセッサに対するページテーブルおよび                                       |      |

|     | 7.3. 複数のプロセッケに対するペーンナーブルおよび ページ・ディレクトリ・エントリの変更の伝搬                 | 7-16 |

|     | 7.4. シリアル化命令                                                      |      |

|     |                                                                   |      |

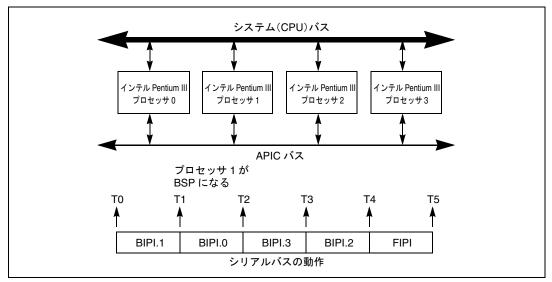

|     | 7.5. マルチプロセッサ (MP) 初期化                                            | 7-18 |

|     | 7.5.1. BSP プロセッサと AP プロセッサ                                        | 7-19 |

|     | 7.5.2. インテル® Xeon™ プロセッサの MP 初期化プロトコルの                            | 7.00 |

|     | 必要条件および制約7.5.3. インテル <sup>®</sup> Xeon™ プロセッサの MP 初期化プロトコルのアルゴリズム | 7-20 |

|     | 7.5.3. インテル® Xeon'™ プロセッサの MP 初期化プロドコルのアルコリスム<br>7.5.4. MP 初期化の例  | 7.20 |

|     | 7.5.4. MP 初期にの例<br>7.5.4.1. 一般的な BSP 初期化シーケンス                     | 7 00 |

|     | 7.5.4.2. 一般的な AP 初期化シーケンス                                         |      |

|     | 7.5.5. MP システム内のプロセッサの識別                                          |      |

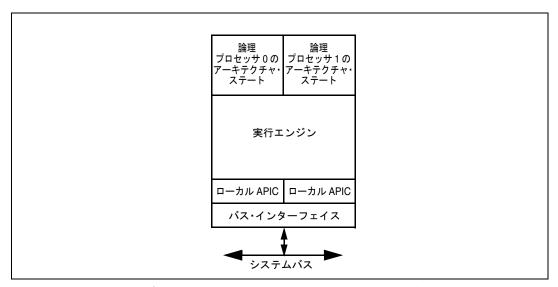

|     | 7.6. ハイパー・スレッディング・テクノロジ                                           |      |

|     | 7.6. ハイハー・スレッティング・テクノロジ                                           | 7 07 |

|     | 7.6.1. ハイハー・スレッティング・テクノロンのアーキテクテャ                                 |      |

|     | 7.6.1.2. APIC の機能                                                 |      |

|     | 7.0.1.2. AFIC VIIX.R                                              | 7 20 |

|     | 7.6.1.4. ページ属性テーブル(PAT)                                |                           |

|-----|--------------------------------------------------------|---------------------------|

|     | 7.6.1.5. マシン・チェック・アーキテクチャ                              |                           |

|     | 7.6.1.6. デバッグレジスタと拡張機能                                 |                           |

|     | 7.6.1.7. 性能モニタリング・カウンタ                                 |                           |

|     | 7.6.1.8. IA32_MISC_ENABLE MSR                          |                           |

|     | 7.6.1.9. メモリ・オーダリング                                    | 7-31                      |

|     | 7.6.1.10. シリアル化命令                                      | 7-31                      |

|     | 7.6.1.11. マイクロコード・アップデートのリソース                          |                           |

|     | 7.6.1.12. 自己修正コード                                      | 7-32                      |

|     | 7.6.2. プロセッサ固有の HT テクノロジ機能                             |                           |

|     | 7.6.2.1. プロセッサ・キャッシュ                                   | 7-32                      |

|     | 7.6.2.2. プロセッサのトランスレーション・ルックアサイド・                      |                           |

|     | バッファ(TLB)                                              |                           |

|     | 7.6.2.3. 温度モニタ                                         |                           |

|     | 7.6.2.4. 外部信号の適合性                                      |                           |

|     | 7.6.3. ハイパー・スレッディング・テクノロジの検出                           |                           |

|     | 7.6.3.1. MONITOR/MWAIT 命令のサポートの検出                      |                           |

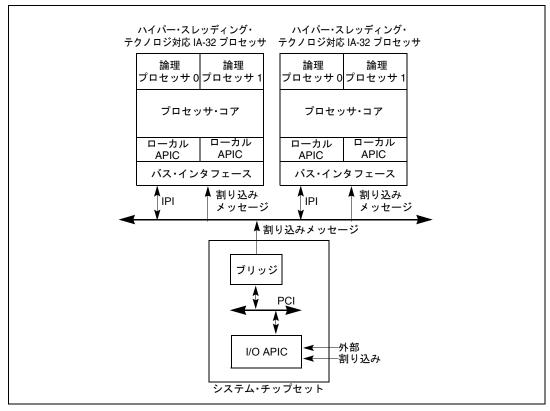

|     | 7.6.4. ハイパー・スレッディング・テクノロジ対応 IA-32 プロセッサの初期化            | 7-35                      |

|     | 7.6.5. ハイパー・スレッディング・テクノロジ対応 IA-32 プロセッサ上の              |                           |

|     | 複数のスレッドの実行                                             | 7-36                      |

|     | 7.6.6. ハイパー・スレッディング・テクノロジ対応 IA-32 プロセッサ上の              |                           |

|     | 割り込みの処理                                                |                           |

|     | 7.7. アイドル状態とブロック状態の管理                                  | 7-38                      |

|     | 7.7.1. HLT 命令                                          | 7-38                      |

|     | 7.7.2. PAUSE 命令                                        |                           |

|     | 7.7.3. MONITOR/MWAIT 命令                                | 7-39                      |

|     | 7.7.4. Monitor/Mwait のアドレス範囲の決定                        |                           |

|     | 7.7.5. MP システム内の論理プロセッサの識別                             | 7-42                      |

|     | 7.7.6. 必要なオペレーティング・システムのサポート                           |                           |

|     | 7.7.6.1. spin-wait ループ内での PAUSE 命令の使用                  | 7-47                      |

|     | 7.7.6.2. アイドル状態の論理プロセッサのホルト                            |                           |

|     | 7.7.6.3. 複数の論理プロセッサ上のスレッドのスケジューリングの                    |                           |

|     | ガイドライン                                                 | 7-50                      |

|     | 7.7.6.4. 実行ベースのタイミング・ループの除去                            | 7-50                      |

|     | 7.7.6.5. アライメントされた 128 バイト・メモリ・ブロック内への                 |                           |

|     | ロックとセマフォの配置                                            | 7-51                      |

|     |                                                        |                           |

| 笋Ω音 | アドバンスド・プログラマブル割り込みコントローラ (APIC)                        | Q_1                       |

| おり早 |                                                        |                           |

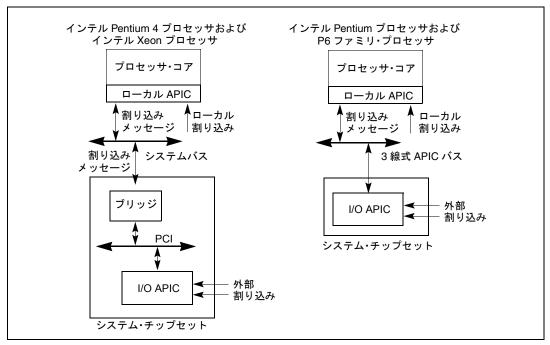

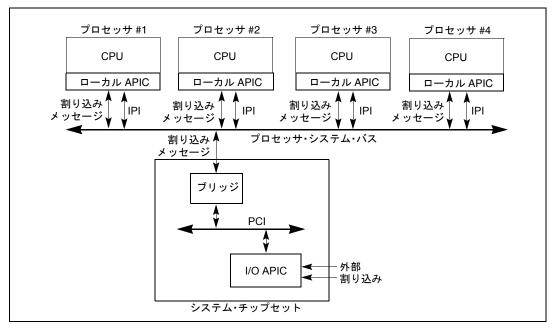

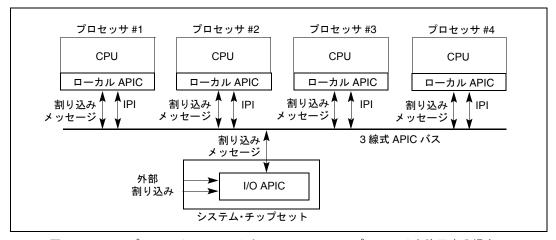

|     | 8.1. ローカル APIC と I/O APIC の概要                          |                           |

|     | 8.2. システムバスと APIC バス                                   | 8-6                       |

|     | 8.3. インテル® 82489DX 外部 APIC、APIC、xAPIC の関係              | 8-6                       |

|     | 8.4. ローカル APIC                                         |                           |

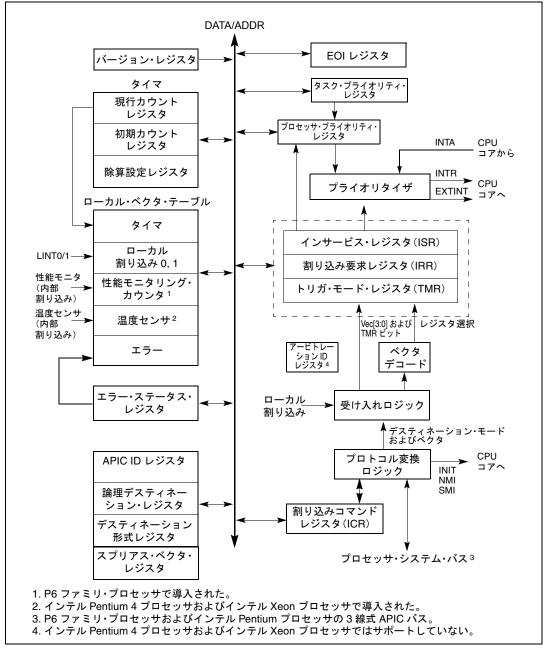

|     | 8.4.1. ローカル APIC のブロック図                                | 9-7                       |

|     | 8.4.2. ローカル APIC の有無                                   |                           |

|     | 8.4.3. ローカル APIC の有無                                   | 0-10<br>8 <sub>-</sub> 11 |

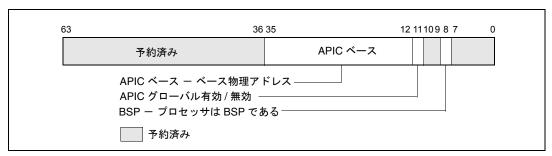

|     | 8.4.4. ローカル APIC のステータスと位置                             |                           |

|     | 8.4.5. ローカル APIC レジスタの再配置                              |                           |

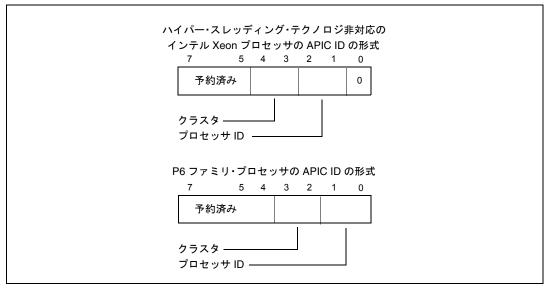

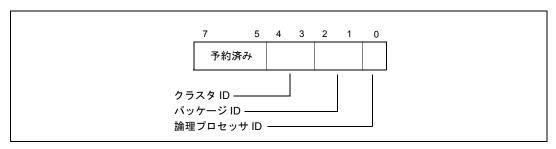

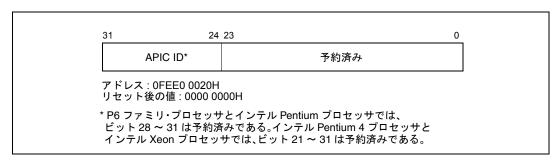

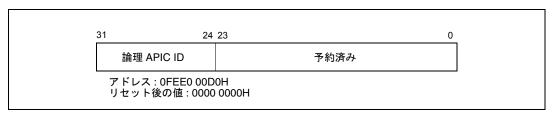

|     | 8.4.6. ローカル APIC ID                                    |                           |

|     | 8.4.7. ローカル APIC の状態                                   |                           |

|     | 8.4.7.1. 電源投入またはリセット後のローカル APIC の状態                    | 0-14<br>Ω_1/              |

|     | 8.4.7.2. ソフトウェア的に無効にされたローカル APIC の状態                   |                           |

|     | 8.4.7.3. INIT リセット後のローカル APIC の状態 ("wait-for-SIPI" 状態) |                           |

|     | 8.4.7.4. INIT デアサート IPI 受信後のローカル APIC の状態              |                           |

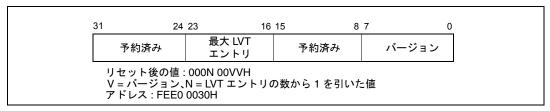

|     | 8.4.8. ローカル APIC バージョン・レジスタ                            | Ω-13<br>21-Ω              |

|     |                                                        |                           |

|     | 8.5. ローカル割り込みの処理                                       | 8-16                      |

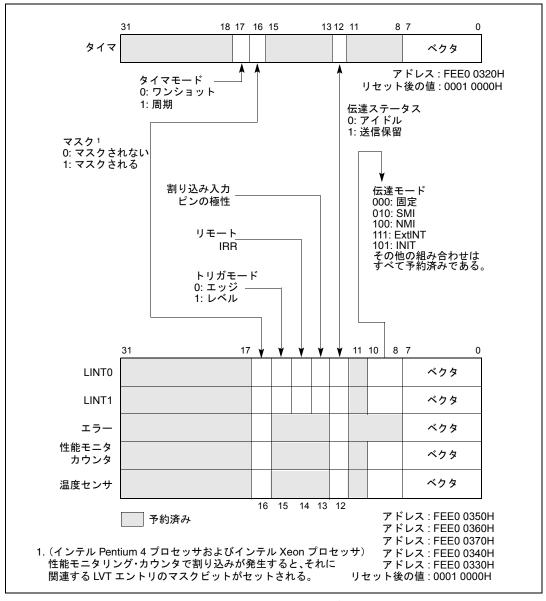

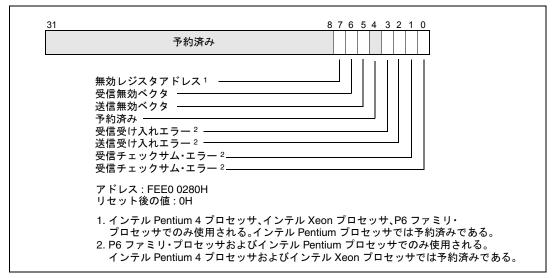

|     | 8.5.1. ローカル・ベクタ・テーブル                                   |                           |

|     | 8.5.2. 有効な割り込みベクタ                                      |                           |

|     | 8.5.3. エラー処理                                           | 8-21                      |

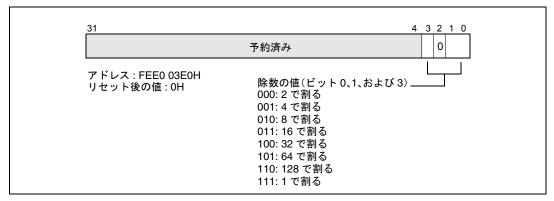

|     |      |         | APIC タイマ                                    |              |

|-----|------|---------|---------------------------------------------|--------------|

|     |      | 8.5.5.  | ローカル割り込みの受け入れ                               | 8-24         |

|     | 8.6. | プロセ     | ッサ間割り込みの発行                                  | 8-24         |

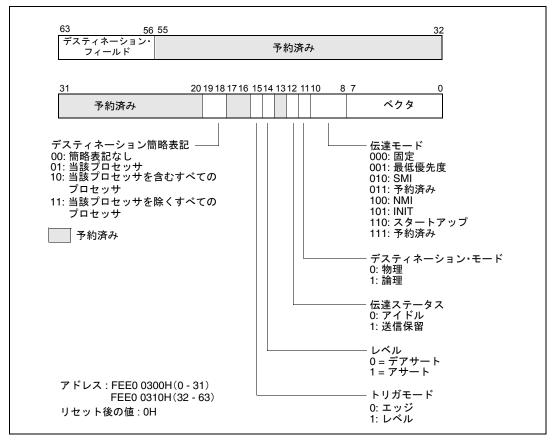

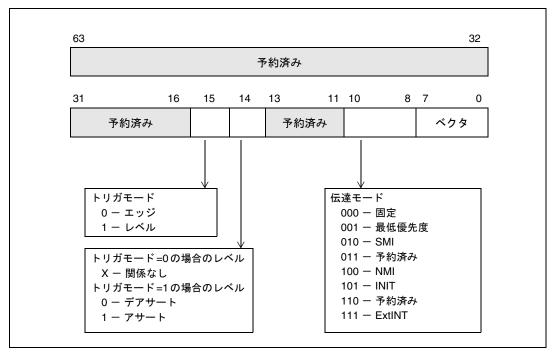

|     |      | 8.6.1.  | 割り込みコマンドレジスタ (ICR)                          | 8-24         |

|     |      | 8.6.2.  | IPI のデスティネーションの指定                           | 8-30         |

|     |      |         | 8.6.2.1. 物理デスティネーション・モード                    | 8-3          |

|     |      |         | 8.6.2.2. 論理デスティネーション・モード                    |              |

|     |      |         | 8.6.2.3. ブロードキャスト/自己伝達モード                   |              |

|     |      |         | 8.6.2.4. 最低優先度伝達モード                         |              |

|     |      |         | IPI の伝達と受け入れ                                |              |

|     |      |         | ムバスと APIC バスのアービトレーション                      |              |

|     | 8.8. | 割り込     | みの処理                                        | 8-37         |

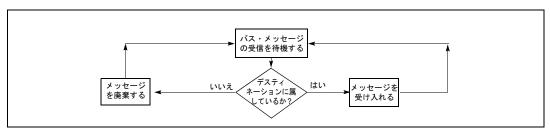

|     |      | 8.8.1.  | インテル® Pentium® 4 プロセッサおよびインテル® Xeon™ プロセッサの |              |

|     |      |         | 割り込み処理                                      | 8-37         |

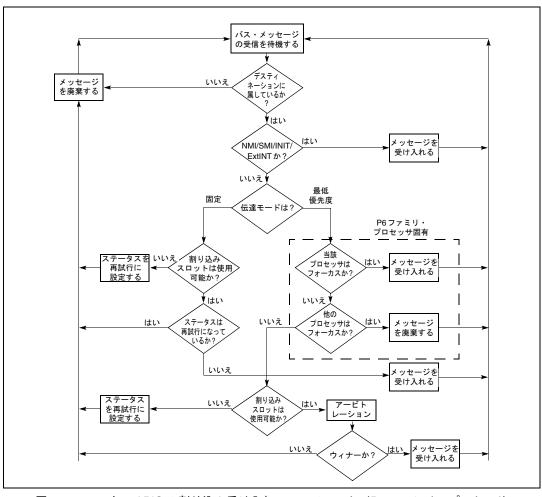

|     |      | 8.8.2.  | P6 ファミリ・プロセッサおよびインテル® Pentium® プロセッサの       |              |

|     |      | 0.00    | 割り込み処理                                      | 8-38         |

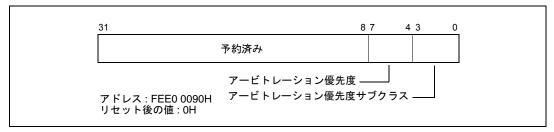

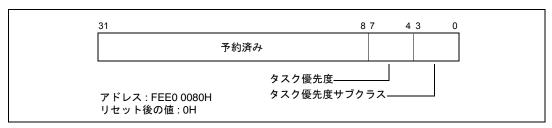

|     |      | 8.8.3.  | 割り込み、タスク、プロセッサの優先度                          | 8-40         |

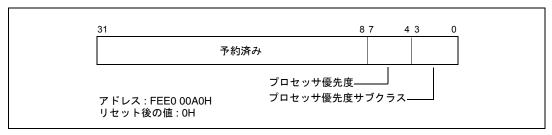

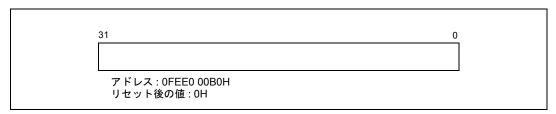

|     |      | 001     | 8.8.3.1. タスク優先度とプロセッサ優先度                    |              |

|     |      | 0.0.4.  | 固定割り込みの受け入れ割り込みサービス完了の通知                    | 8-42         |

|     |      |         |                                             |              |

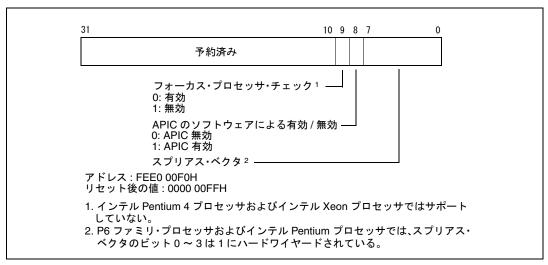

|     |      |         | アス割り込み                                      | 8-45         |

|     | 8.10 |         | バス・メッセージの受け渡し機構およびプロトコル                     |              |

|     |      |         | ァミリ・プロセッサおよびインテル® Pentium® プロセッサのみ)         |              |

|     |      |         | バス・メッセージの形式                                 |              |

|     | 8.11 | .メッセ    | ージ・シグナル割り込み                                 | 8-47         |

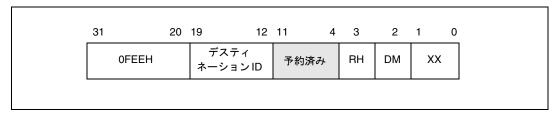

|     |      |         | メッセージ・アドレス・レジスタの形式                          |              |

|     |      | 8.11.2. | . メッセージ・データ・レジスタの形式                         | 8-50         |

|     |      |         |                                             |              |

| 第9章 | プロ   | コセッ     | サの管理と初期化                                    | 9-1          |

|     | 9.1. | 初期化     | の概要                                         | 9-           |

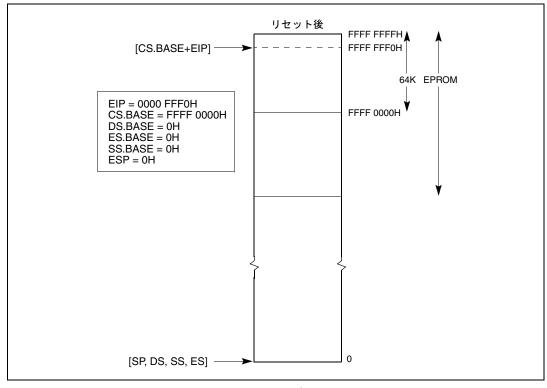

|     |      | 9.1.1.  | リセット後のプロセッサの状態                              | 9-3          |

|     |      | 9.1.2.  | プロセッサ・ビルトイン・セルフ・テスト                         |              |

|     |      |         | (BIST: Processor Built-in Self-test)        | 9-3          |

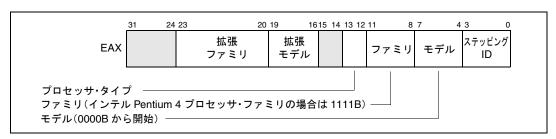

|     |      |         | モデルとステッピングに関する情報                            |              |

|     |      |         | 最初に実行される命令                                  |              |

|     | 9.2. |         | PU の初期化                                     |              |

|     |      | 9.2.1.  | x87 FPU 環境の構成                               | 9-8          |

|     |      |         | x87 FPU ソフトウェア・エミュレーションに対するプロセッサの設定         |              |

|     | 9.3. | キャッ     | シュのイネーブル                                    | 9-9          |

|     | 9.4. | モデル     | 固有レジスタ(MSR)                                 | 9-10         |

|     |      |         | タイプ範囲レジスタ(MTRR)                             |              |

|     |      |         | SSE2、SSE3 の拡張命令の初期化                         |              |

|     |      |         | レスモード動作に対するソフトウェア初期化                        |              |

|     | 9.7. |         | 実アドレスモード IDT                                |              |

|     |      | 9.7.1.  | メディンスモート 101                                | 9-12<br>0-19 |

|     | 0.0  | -       | ード動作に対するソフトウェア初期化                           |              |

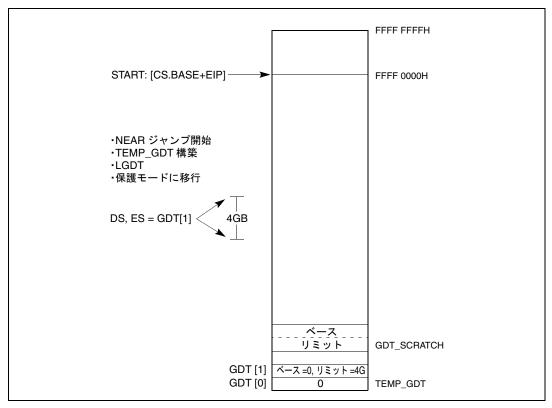

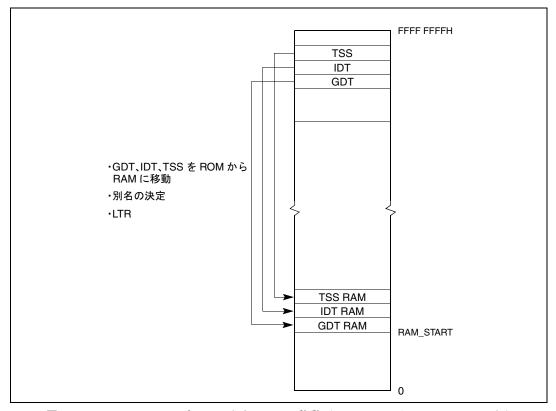

|     | 9.8. |         | ート動作に対するフラトウェア初知化<br>保護モードシステムのデータ構造        |              |

|     |      | 9.0.1.  | 保護モードンペナムのナーテ備は                             | 9-12<br>Q-12 |

|     |      |         | ページングの初期化                                   |              |

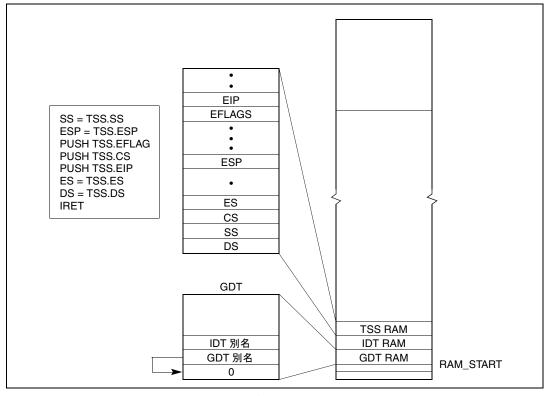

|     |      | 9.84    | マルチタスキングの初期化                                | 9-16         |

|     | 0.0  |         | 切り替え                                        |              |

|     | ອ.ອ. | 991     | 切り替え<br>保護モードへの切り替え                         | 9-17         |

|     |      | 9.9.2   | 実アドレスモードへの再切り替え                             | 9-18         |

|     | 9 10 |         | とモード切り替えの例                                  |              |

|     | 9.10 |         | ・アセンブラの使用                                   |              |

|     |      |         | 、アセファフの使用<br>STARTUR ASM IIフト               | 0-22         |

|                    | 9.10.3. MAIN.ASM ソースコード                                                          |                  |

|--------------------|----------------------------------------------------------------------------------|------------------|

|                    | 9.10.4. サポートするファイル                                                               |                  |

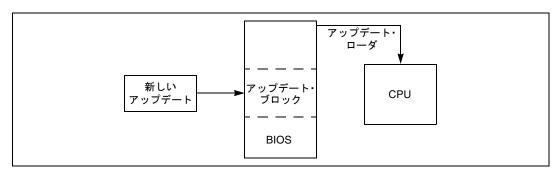

|                    | 9.11. マイクロコード・アップデート機能                                                           | 9-34             |

|                    | 9.11.1. マイクロコード・アップデート                                                           | 9-34             |

|                    | 9.11.2. オプションの拡張シグネチャ・テーブル                                                       | 9-39             |

|                    | 9.11.3. プロセッサの識別                                                                 | 9-40             |

|                    | 9.11.4. プラットフォームの識別                                                              | 9-41             |

|                    | 9.11.5. マイクロコード・アップデートのチェックサム                                                    |                  |

|                    | 9.11.6. マイクロコード・アップデート・ローダ                                                       | 9-43             |

|                    | 9.11.6.1. アップデートのロードに対するハードリセットの影響<br>9.11.6.2. マルチプロセッサ・システム内のアップデート            | 9-44             |

|                    | 9.11.6.2. マルナフロゼッサ・システム内のアッフテート<br>9.11.6.3. HT テクノロジ対応システム内のアップデート              | 9-44             |

|                    | 9.11.6.4. アップデート・ローダの拡張                                                          |                  |

|                    | 9.11.7. アップデートのシグネチャと検証                                                          | <del>9-4</del> 5 |

|                    | 9.11.7.1. シグネチャの確認                                                               |                  |

|                    | 9.11.7.2. アップデートの認証                                                              |                  |

|                    | 9.11.8 インテル® Pentium® 4 プロセッサーインテル® Yeon™ プロセッサ                                  |                  |

|                    | P6 ファミリ・プロセッサのマイクロコード・アップデートの仕様                                                  | 9-48             |

|                    | 9.11.8.1. BIOS の役割                                                               | 9-49             |

|                    | 9.11.8.2. コール元プログラムの役割                                                           | 9-52             |

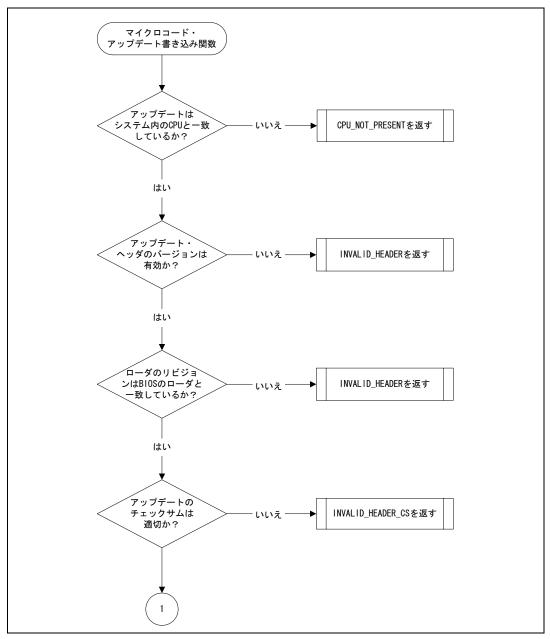

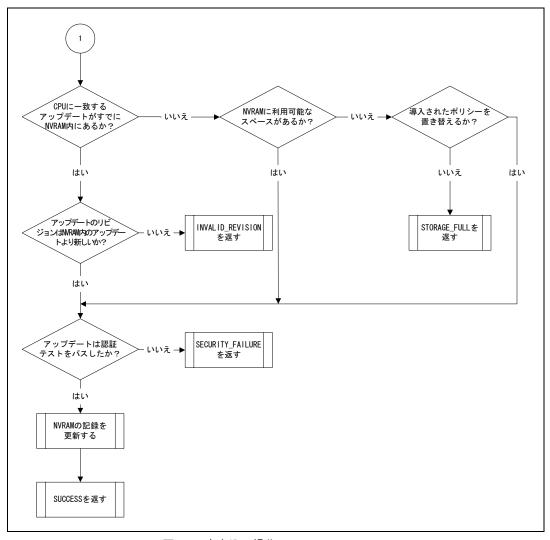

|                    | 9.11.8.3. マイクロコード・アップデート関数                                                       | 9-55             |

|                    | 9.11.8.4. INT 15H ベースのインターフェイス                                                   | 9-55             |

|                    | 9.11.8.5. 関数 00H - 存在テスト                                                         | 9-56             |

|                    | 9.11.8.6. 関数 01H - マイクロコード・アップデート・データ書き込み                                        | 9-56             |

|                    | 9.11.8.7. 関数 02H - マイクロコード・アップデート制御<br>9.11.8.8. 関数 03H - マイクロコード・アップデート・データ読み取り | 9-62             |

|                    | 9.11.8.8. 関致 03日 - マイクロコート・アップテート・データ読み取り<br>9.11.8.9. リターンコード                   | 9-63             |

|                    | 9.11.0.9. 77 24 F                                                                | 9-03             |

| ** 40 <del>*</del> | オテローナ・・・・ 生!!你!!                                                                 | 40.4             |

| 弗 IU 早             | メモリ・キャッシュ制御                                                                      |                  |

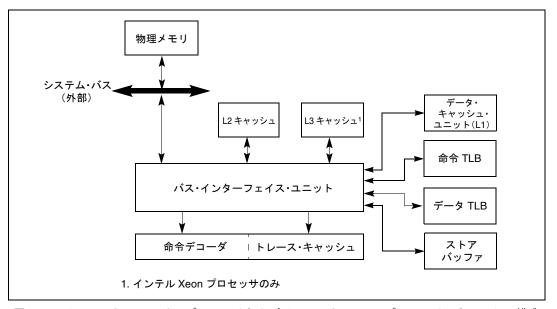

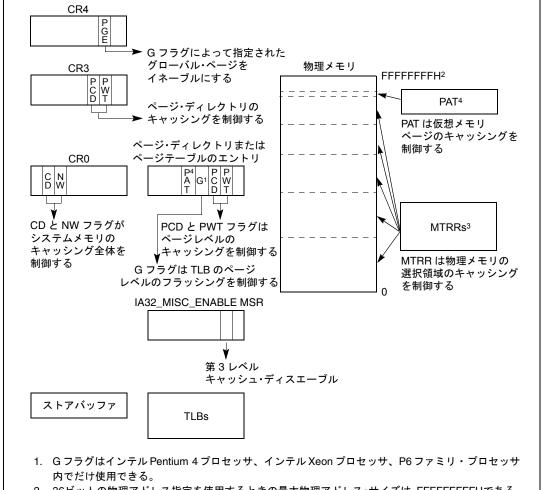

|                    | 10.1.内部キャッシュ、TLB、バッファ                                                            |                  |

|                    | 10.2.キャッシングの用語                                                                   | 10-6             |

|                    | 10.3. 有効なキャッシングの方法                                                               | 10-7             |

|                    | 10.3.1. ライト・コンバイニング・メモリ位置のバッファリング                                                |                  |